NB3L83948C

Overview

- 2.5 V / 3.3V (VDD = VDDO) or

- 3 V VDD / 2.5 V VDDO Operation: 2.5 $5%, 2.375 to 2.625 V 3.3 $5%; 3.135 to 3.465 V

- 350 MHz Clock Support

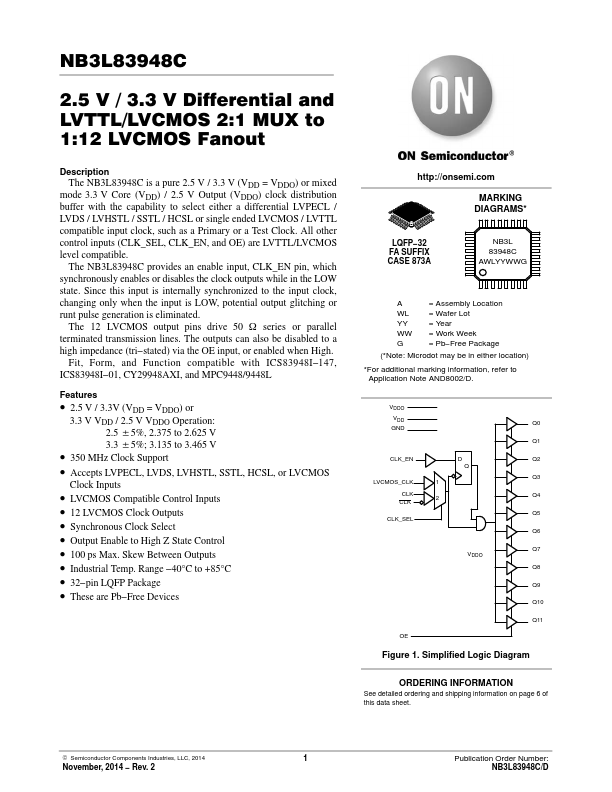

- Accepts LVPECL, LVDS, LVHSTL, SSTL, HCSL, or LVCMOS Clock Inputs

- LVCMOS Compatible Control Inputs

- 12 LVCMOS Clock Outputs

- Synchronous Clock Select

- Output Enable to High Z State Control

- 100 ps Max. Skew Between Outputs

- Industrial Temp. Range -40°C to +85°C